5 纳米制程之后的晶体管应该是什么样?英特尔展示了真正的技术。

两种晶体管一起造——英特尔正在研究的晶体管堆叠技术将大幅度提高芯片的计算密度。目前我们所熟知的台积电、三星、英特尔、格芯、中芯国际等芯片代工厂量产的先进工艺普遍采用基于多栅鳍型场效应晶体管(FinFET)结构。在 5 纳米及以下的制程时,更先进的技术节点面临的发热和漏电将变得难以控制,人们必须寻找全新的工艺,堆叠晶体管设计正在成为重要方向。

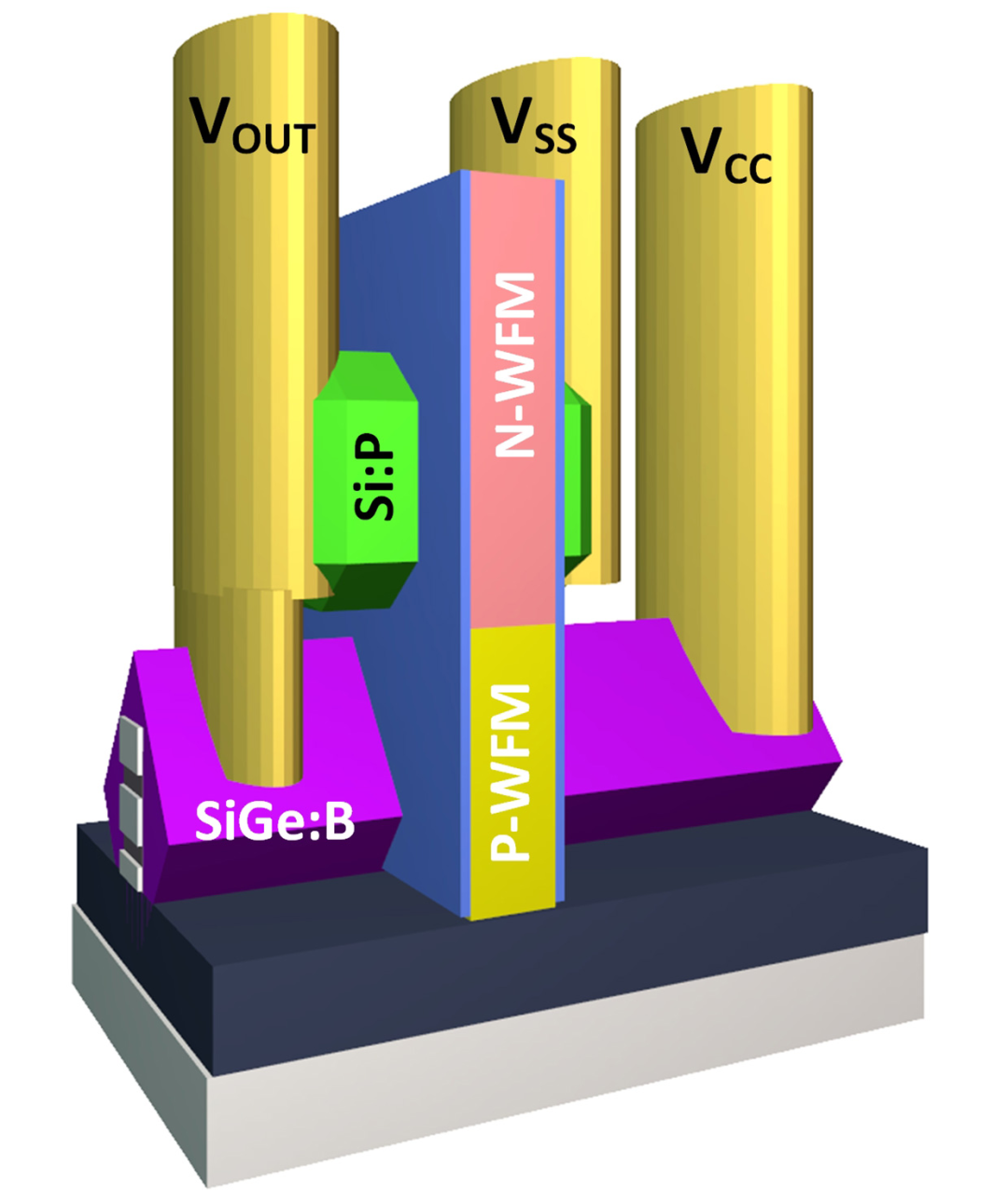

NMOS 和 PMOS 组件通常是并列出现在芯片上的。英特尔现在已经找到了让它们彼此堆叠的方法,这可以大幅度降低电路尺寸。当今几乎所有电子设备的算力本质都是两种晶体管的组合——NMOS 和 PMOS。当电压信号输入时,其中一个打开则另一个会被关闭,两者放在一起时,只有 bit 变化才有电流,这种设计显著降低了能耗。这种晶体管组合自 1959 年以来几乎没有变化,但随着芯片制造制程的不断提升,电路正在不断被缩小,它们之间的距离也在不断靠近。在本周 IEEE 国际电子设备会议(IEDM)上,英特尔展示了一种全新的方式:将 NMOS 和 PMOS 对堆叠起来,该方案有效地将简单 CMOS 电路的占位面积减少了一半,这意味着未来 IC 的晶体管密度可能直接翻倍。

这种设计被广泛认为会首先被应用于下一代制程晶体管即 nanosheet、nanoribbon(纳米薄片)、nanowire(圆柱体纳米线),或被称为全环绕栅极晶体管(Gate-All-Around FET)的方法上,这可能是常规架构计算机通向摩尔定律的最后一步。nanosheet 的沟道区域不会是像目前 FinFET 等方式,由垂直硅鳍片构成晶体管主要部分,而是由多层、水平、几纳米厚的片层堆叠在一起构成。

CMOS 设备已经从平面发展到 FinFET,马上就将在 3nm 制程节点上转为 nanosheet。进一步缩小的电路需要堆叠 NMOS 和 PMOS。

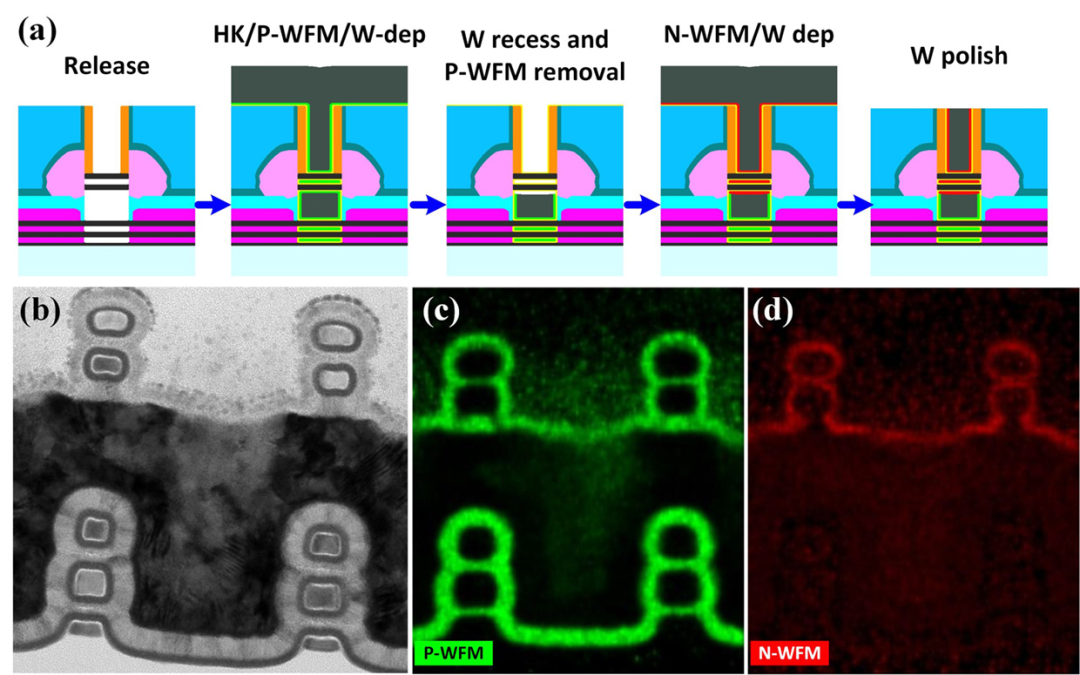

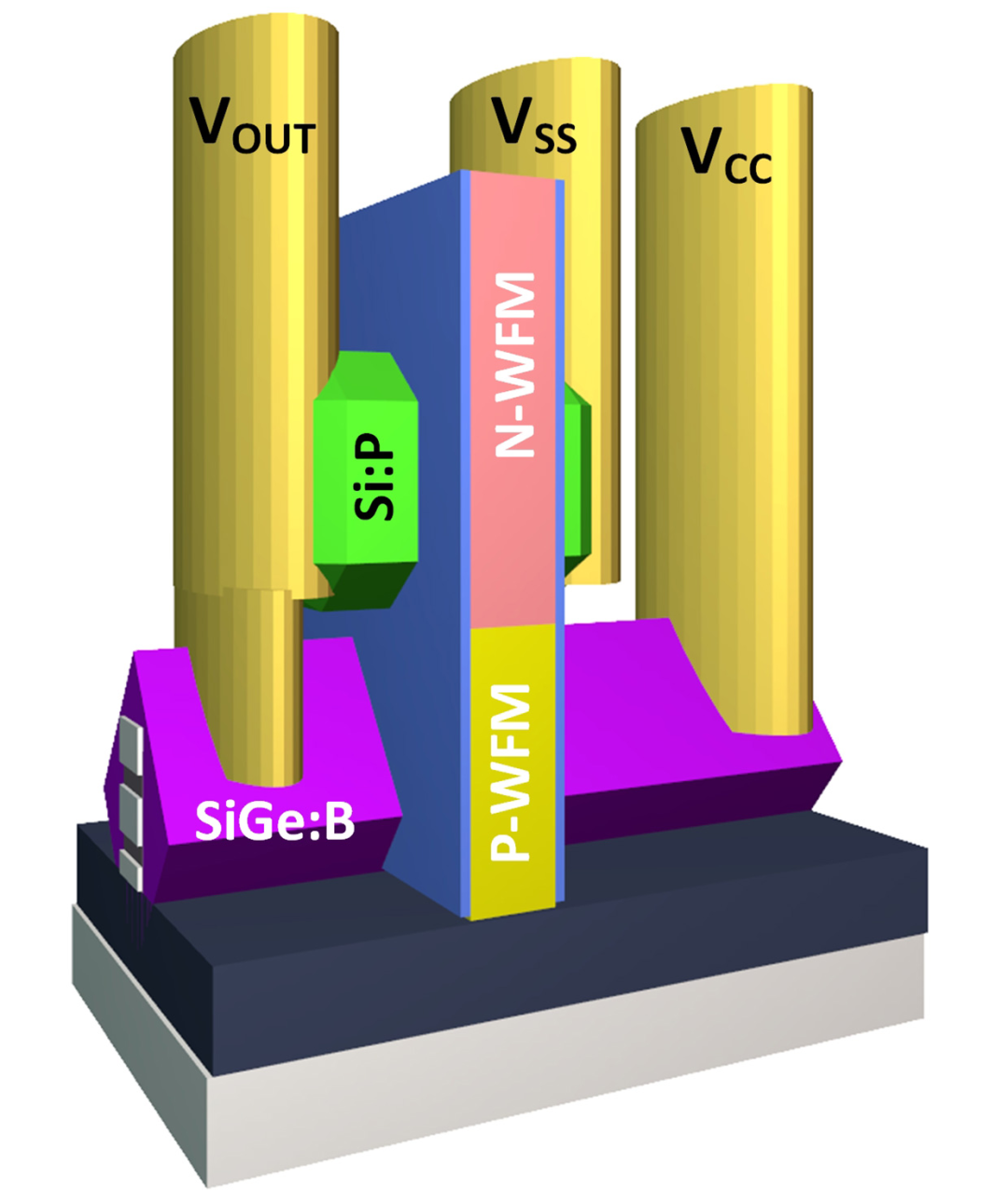

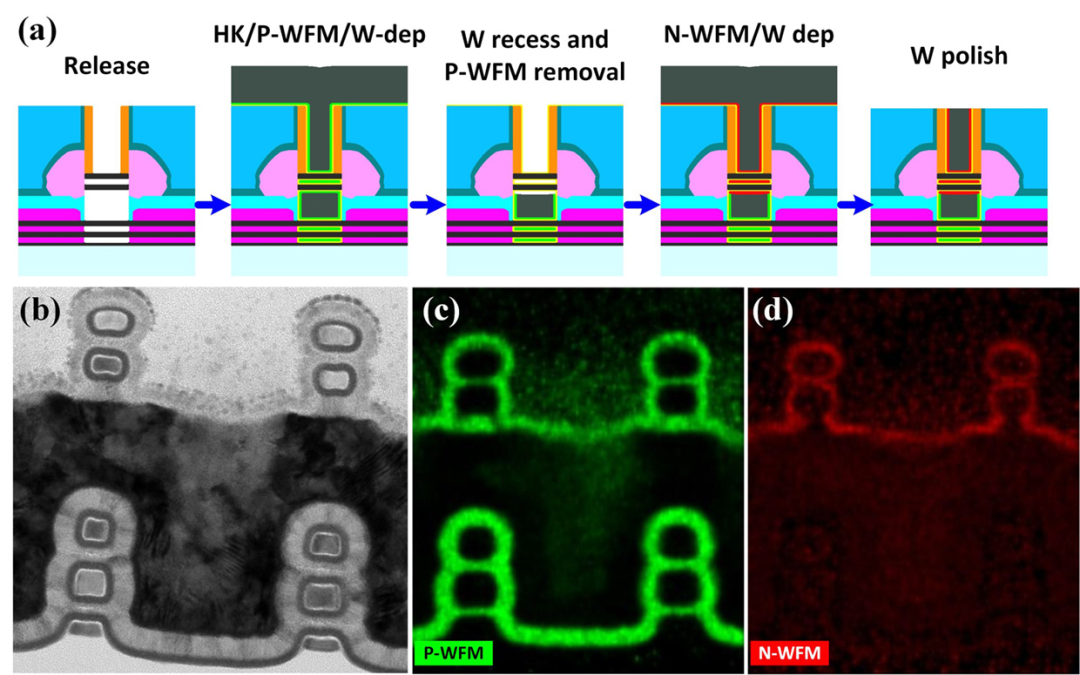

英特尔的工程师打算使用这些组件来构建最简单的 CMOS 逻辑电路,即逆变器(inverter)。它需要由两个晶体管组成,两个电源连接,一个输入和一个输出连接。即使是像今天晶体管并排放置的设计中,这种布局也已非常紧凑了。但通过堆叠晶体管,调整互联,逆变器的面积还可以减半。英特尔用于构建堆叠式 nanosheet 的方法被称为自对准工艺,因为它可以在实际上相同的步骤中构建两种组件。这是至关重要的一点,因为假如出现第二种步骤的话(例如在互相分离的晶片上制造两种组件再粘合),可能会导致无法对准,进而失败。从本质上讲,晶体管堆叠技术是对 nanosheet 晶体管制造方式的修改。它从硅和硅锗的重复层开始,随后将其雕刻成一个较高的窄鳍,然后蚀刻掉硅锗,留下一组悬浮的 nanosheet。通常,所有的 nanosheet 都会形成单独的晶体管。但是在新方法中,为了形成一个 NMOS 器件,顶部的两个 nanosheet 被连接到了磷掺杂的硅上,而底部的两个 nanosheet 被连接到了硼掺杂的硅锗上以产生 PMOS。「完整的『集成流程』当然会更加复杂,但英特尔的研究者们正希望让工艺尽可能地简单,」英特尔高级研究员、组件研究主管 Robert Chau 表示。「集成流程不能太复杂,因为这将影响到制造具有堆叠 CMOS 芯片的实用性。这是一个非常实际的流程,可产生可观的结果。」

逆变器由两个彼此叠置的晶体管组成,它们的某些部分和互连点是公用的。「一旦你掌握了这种方法,接下来要做的就是追求性能了,」Chau 说道。这可能将涉及改进的 PMOS 组件,目前它在驱动电流的能力上落后于 NMOS。解决这个问题的答案可能在于在晶体管通道中引入「应变」,其思路是让硅晶格变形,从而为电载荷创造更快的通路(此处为孔洞)。英特尔早在 2002 年就将应变方法引入其芯片。在另一项 IEDM 的研究中,英特尔展示了一种在 nanoribbon 晶体管中产生压缩应变和拉伸应变的方法。除了英特尔之外,其他顶尖芯片工厂和研究机构也在寻求堆叠式的 nanosheet 设计,当然有些时候类似的方法会被命名为互补 FET 或纳米薄片场效应晶体管(CFET)。比利时研究组织 Imec 率先提出了 CFET 概念,并于去年 6 月在 IEEE VLSI 研讨会上报告了构建它们的过程。不过,Imec 组件并非完全由 nanosheet 晶体管构成——它的底层由 FinFET 组成,顶层是单个 nanosheet。来自台湾省的半导体研究中心(Taiwan Semiconductor Research Institute, TSRI)研究人员提出了另一种 CFET 的生产方法,其 PMOS 和 NMOS 需要用不同的 nanosheet 制造出来。英特尔的电路在三个 nanosheet PMOS 上有两个 NMOS,相比之下更接近于堆叠组件的概念。https://spectrum.ieee.org/nanoclast/semiconductors/devices/intels-stacked-nanosheet-transistors-could-be-the-next-step-in-moores-lawhttps://spectrum.ieee.org/semiconductors/devices/the-nanosheet-transistor-is-the-next-and-maybe-last-step-in-moores-law© THE END

转载请联系本公众号获得授权

投稿或寻求报道:content@jiqizhixin.com

关注公众号:拾黑(shiheibook)了解更多

[广告]赞助链接:

四季很好,只要有你,文娱排行榜:https://www.yaopaiming.com/

让资讯触达的更精准有趣:https://www.0xu.cn/

关注网络尖刀微信公众号

关注网络尖刀微信公众号

机器之心

机器之心